Here's my full testbench setup. On the upper left, I have a 156V DC power supply. On the lower-left sits a 12V battery to act as an accessory battery. The 30Mhz $400 oscilloscope sits ready. The opened up DC-DC converter is front and center. I have the oscope covered with cardboard to shield out excess light so I can take pictures of waveforms. I actually used the aluminum case for the DC-DC converter as a camera stand so that I could turn off the flash which causes too much glare on the oscope screen.

Here's a close-up view of the 156V power supply. In essence, I took five 31.2 volt power supplies from HP inkjet printers and hooked them up in series. I broke off the grounding pin of all the power cords except the bottom supply so that the output stage could float and allow the series connection. These supplies put out 2.5 amps, so this ought to provide 375 watts of power if I need it for testing.

Okay, here's the first scope trace. I removed the blown FETs and simply measured Vgs at the missing part location. Dimensions are 5us/div and 5V/div. It looks like we have a period of 30us and the power supply for the SG3525A is 12 volts. Without the FETs in place the controller drives both FETs in push-pull configuration at their full duty cycle. There's actually a dead time of about 0.6us between the high states on the gate-drive pulses.

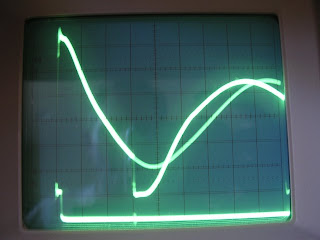

I've just soldered in two IRFP460 FETs (still with no load on the output) and here's what the gate-drive looks like. The pulse from the SG3525A is on the bottom and the actual Vgs voltage at the FET is the top waveform. The IRFP460 part has a larger gate capacitance than the original IRFP350 parts, so the charge and discharge slope doesn't look so great. Perhaps I could reduce the resistance of the gate-drive resistors to help with this. The FETs are still cold with no load. With the FET in place, the drive pulse shortens to 0.9us. Dimensions are 0.5us/div and 5V/div.

Here's where things get interesting. I'm now measuring the drain-source voltage on one of the FETs (Vds) with no output load. Dimensions are 20us/div and 50V/div. Without any load, the voltage swings on the FETs are twice the input voltage (about 312 volts) plus any ringing from inductor kick-back! One of the disadvantages of the push-pull architecture is that the driving transistors need to handle twice the input voltage.

The far left of the screen shows one FET turning off and letting the voltage oscillate. The two high spikes near the right edge of the screen show the voltage across the first FET as the second FET turns on. There's even over-voltage from the inductive ringing. If the input voltage goes up to 170V with charging and regenerative braking, the FETs need to handle at least 340 volts plus the ringing voltage, which is typically even higher... (yikes!)

I've added the 12V accessory battery as an output load and let things settle. This picture shows the gate drive (Vgs) of one FET (bottom left) and the resulting source-drain voltage (Vds) on the opposite FET. Time dimension is 5us/div. Note that the pulses going to the FET gates are 15us apart, causing the snap to a low voltage three divisions into the display. The Vgs pulse is still about 1.2 usec wide.

Here's the same image as above, but with a 7 amp load. The SG3525A is now pulsing the FETs much more often to handle the load. The gate-drive pulses are now 8us wide and the drain-source voltages are clearly jumping from zero volts to 156 volts to 312 volts.

The circuit controlling this pulse width is the opto-coupler feedback going into the inverting input on the SG3525A. As the load increases, the main output voltage tends to drop, telling the 741 op-amp to turn off the 4N25 opto-coupler. With the opto-coupler off, the inverting input for the error amplifier in the SG3525A falls and increases the pulse width. (See schematic in previous blog posting)

What boggles me about this picture is that this DC-DC converter was supposed to put out 400 watts. That's about 28 amps. Just pulling 7 amps causes the gate drive pulse width to increase to 8us which is over half of the available 15us time that they can be on. If I add another 7 amp load, the gate pulse width extends out to its full width of 15us and then the waveforms go a bit nuts. It seems to me that if we run out of controllable pulse width at 14 amps, then the controller has no way of providing anywhere near 28 amps. Hmm....

Another circuit I analyzed was the amperage control circuit. This circuit captures current going through the isolation transformer and converts it to voltage pulses. If these pulses get too high then the SG3525A controller should turn off the FET gate drives to prevent them from overheating. The top waveform in the above picture shows the voltage across the "Amps Adjust" potentiometer with just the 12V accessory battery load. Note that the primary signal shows nice rolling pulses; however, there are sharp spikes at every gate drive transition. These rolling pulses are supposed to control the nShutdown pin on the SG3525A controller. The unfortunate thing is that the actual voltage triggering the nShutdown pin are the voltage spikes. I believe the dimensions are 0.5V/div for the top waveform and 5us/div timebase.

Here's that same picture with a 7 amp load. The bottom waveform shows the FET gate drive pulses widening out to 8us and the voltage on the "amps adjust" pot show a much higher voltage (with much higher spikes too). I really need to get rid of those spikes.

I'm unsure of where to go next. It's clear to me that the 312 volts across the FETs along with the inductive kick-back spikes are running very near to the operating point of the FETs. At high current pulls, the inductive spikes are only going to get worse and tend to blow the FETs. I'm also concerned that a 7 amp load consumes just over 50% of the available pulse width modulation range for the gate-drive pulses, so we just can't supply more than about 13 amps without maxing out.

My first step is to try and reduce the inductive spiking. The only circuit provided for that is the C7/R16 capacitor/resistor pair between the FET drain posts. I found a great article on how to pick these values on the Maxim website here:

http://www.maxim-ic.com/appnotes.cfm/an_pk/3835

I also might add an RC filter to the "amps adjust" circuit to filter out the high-voltage spikes so that the nShutdown input gets a more accurate voltage.

I still haven't heard back from CCpower about this, but I'll give them a few more days. As you might imagine, I'm rather frustrated that I have to debug someone else's design. I'm not sure this component was meant for this application.

2 comments:

Hi Tim,

Couple of comments for you.

The ringing waveform on the drain of the FETs is normal at light loads. This is because the converter is running in discontinuous current mode. As you increase the load you will see the waveform straighten up.

The duty cycle or pulse width is not the best indicator of load current. In fact in an ideal circuit the pulse width would not change with load. So don't worry too much about that. The pulse width will change with input voltage though. If you are seeing the pulse width go full on with load you may not be providing enough input voltage. That is the transformer turns ratio is not correct for the application.

Also keep in mind that in a push pull configuration the FETs see twice the input voltage plus whatever ringing exists. So in your application you would want at least 400V FETs and probably should have 500V parts.

There are some much better FETs out there than what is this product. Obviously they cost a bit more and that's why people don't see them in these types of power supplies. Infineon CoolMOS parts come to mind. They have some nice 500 and 600V parts.

Regards,

Chris Brune

Hi Chris. Thanks for the comments. After doing some more measurements under load, I could definitely see that the duty cycle related to voltage, not current. With a supply voltage of 156, I'm definitely getting 312 volt waveforms. If I start driving right at the end of a charge cycle, the pack is up at 170V, making 340V across the FETs (yikes). Fortunately, I replaced the original ones (400V) with 500V ones to help.

Cheers,Tim

Post a Comment